The Future of ASIC Cloud Begins Here

Beyond Imagination

Unfolding the ASIC Cloud Horizon

Powering Innovation: Pioneering Eco-Friendly Shift with an AI Accelerator-Embedded ASIC Platform for Ultra-Low Power Applications

The Coming Revolution in AI Chip

Artemis, the Pinnacle of Hyper-Cloud ASIC Accelerators, is ingeniously crafted for superior speed in processing HPC tasks. Harnessing the power of near-threshold voltage ultra-low power and asynchronous massively parallel processing architecture, it embodies the epitome of cross-layer holistic design optimization.

Embark on an Environmental Odyssey: A Transformative Trajectory in HPC AI ASIC for Carbon Emission Reduction

Leaning into a future of superlative performance, Soteria delivers a compelling 0.275V-based standard cell re-characterization, coupled with ultra-low power analog-to-digital hybrid integration. Our trailblazing performance harvesting technologies, tiling and hardening, are impeccably optimized for the upcoming generation of immersion cooling, primed to run a myriad of AI algorithms in eco-conscious data centers. Experience the cutting-edge of super-low power with Soteria.

Device Centric Accelerator

We are at the forefront of revolutionizing data pre-processing, data augmentation, and near-data inference modeling through our device-centric accelerator. Utilizing vector extensions, we are redefining the boundaries of what’s possible in data processing, bringing about a new era of accelerated efficiency and precision.

Innovate, Integrate, Accelerate: Your HPC AI ASIC Journey Begins from Data Storage

Soteria, impeccably conceived for HPC acceleration, is the embodiment of precision engineering tailored to cater to application-specific datacenters. This innovative solution is designed to flawlessly integrate data accelerators with compute accelerators, specializing in Pipelined ML Training and Near Data Processing (NDP) – the seamless synergy for your sophisticated computing needs.

Transformed Hyper-

Scale Accelerators

for Exascale Computing

Reshaping HDL inspired hyper-scale MPPAs,

crafting practical pathways to exascale computing

The Next

Ultra Low Power

Structure

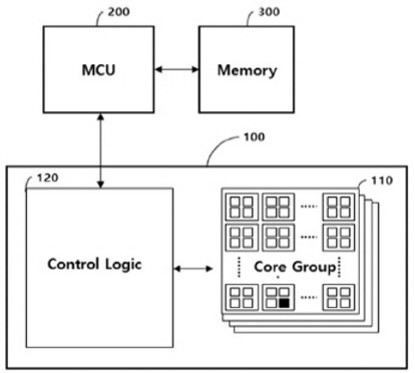

Energy efficiency is maximized by implementing a low-power design methodology and using tidy core structures.

SPEChpc™ HPC Benchmark

AI HPC Processing Array with Industry-Leading Performance

Similar or superior performance compared to the top tire products with lower power requirements.

Artemis, the Pinnacle of Hyper-Cloud ASIC Accelerators, is ingeniously crafted for superior speed in processing HPC tasks. Harnessing the power of near-threshold voltage ultra-low power and asynchronous massively parallel processing architecture, it embodies the epitome of cross-layer holistic design optimization.

The Next Generation.

Device Centric Accelerator

We are at the forefront of revolutionizing data pre-processing, data augmentation, and near-data inference modeling through our device-centric accelerator. Utilizing vector extensions, we are redefining the boundaries of what’s possible in data processing, bringing about a new era of accelerated efficiency and precision

Semiconductor design with the following expertise for a Customer-Centric Culture in Soteria:

Ultra Low-Power Circuit Design

Mixed Signal Designs

Third-Party IPs Integration

AI-Integrated Circuit Design

Quantum Computing Circuit Design

Thermal Dissipation-Aware Design

ESD-Aware Design

Latch-up Aware Design

Metal-Fix Strategy

Spare-Cells Strategy

Near-Data Processing Accelerator

Memory-Centric Architecture Designs

Prefetching High-Speed Interconnect Technology

Scalable Coherent Memory Access

Data Augmentation Modules

CXL-Enabled AI Accelerators

Software-Hardware Co-design

Smart Cache Accelerators

Real-Time Analytics

Dynamic Vector Extension

Our groundbreaking and forward-thinking approach is the powerhouse behind our commitment to fostering a customer-centric culture. We’re not just setting the standard, we’re redefining it, leading the industry into the future with our innovative solutions.

Our Mission

We are the purveyors of an all-inclusive, game-changing vertical solution

Our solution encapsulates data augmentation and goes beyond the mere chip, setting the gold-standard for client experience. Our dexterity in tailoring our service to align with our customers’ AI HPC infrastructure has led to the creation of groundbreaking use cases that have reshaped the landscape across diverse market sectors.

Product Portfolio

Customer Applications

Solutions

Customer Applications

Data Centers(Servers), AI Machine Learning, Cloud Computing, Edge Computing, IOT Data Centers and Cloud Computing, Database and in-memory analytics High Performance Computing (HPC) Networking and Communication Systems

Details

Transforming Green Tech with Workload-Aware Carbon-Neutral ASIC Designs

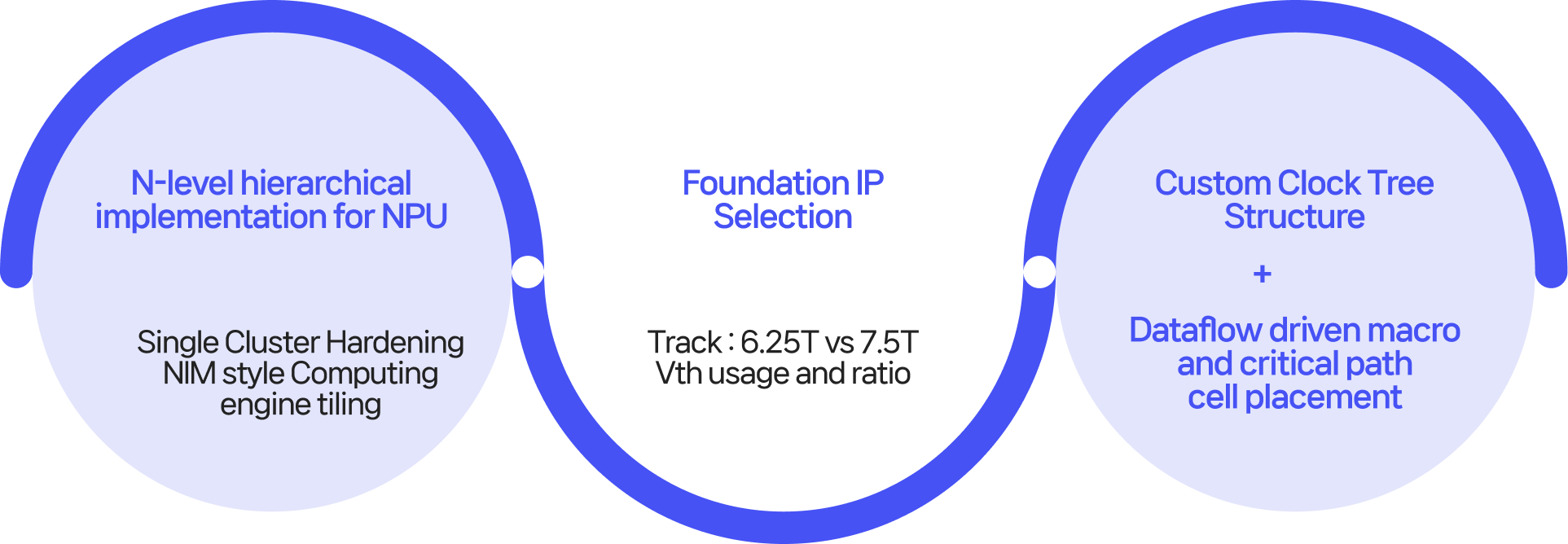

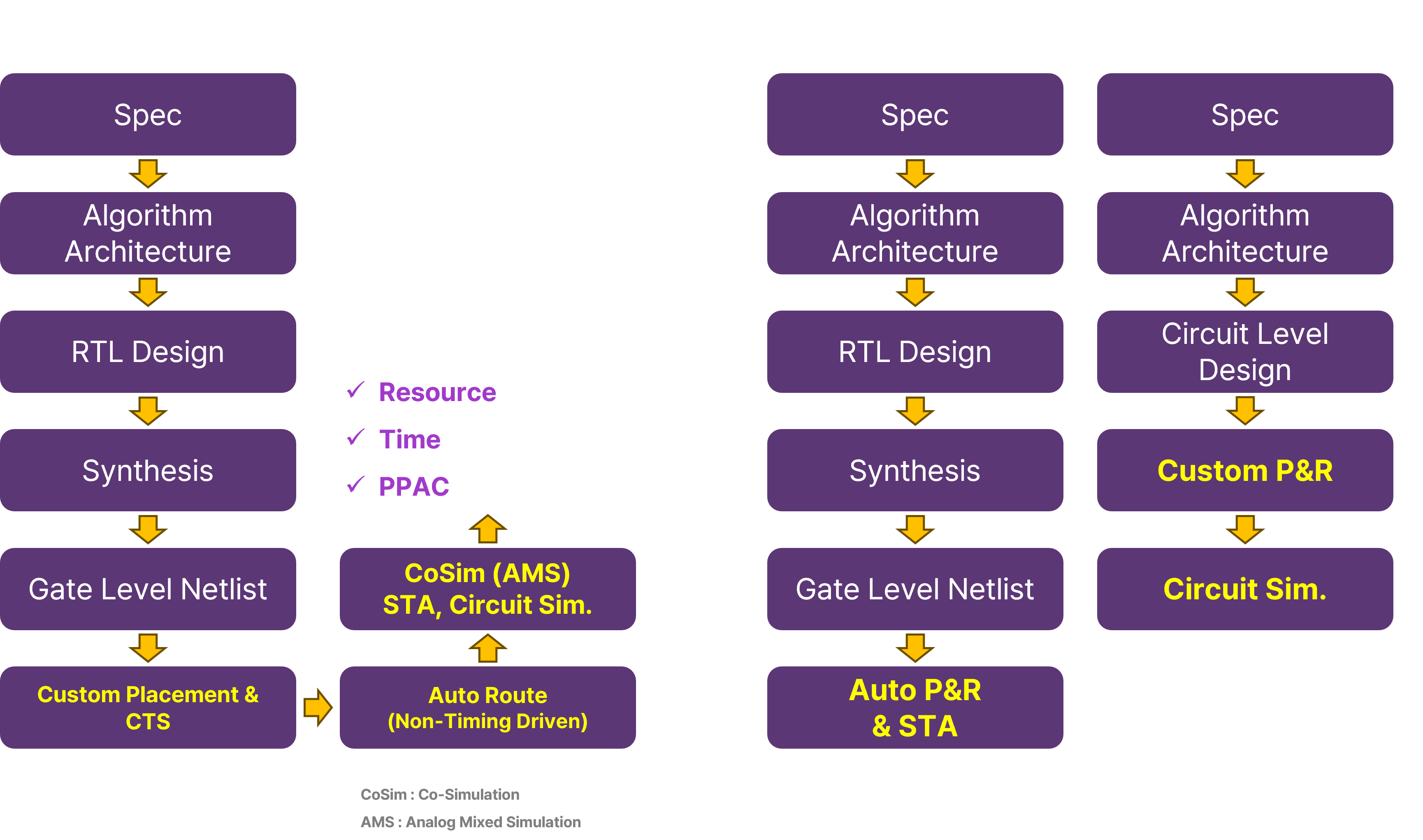

Cross-layer holistic design optimization overcoming the limit of legacy development process

Our Clients

Silicon Valley Research Center, Development Corporation and European Partners

We make green innovation

Meet our eco-friendly technology.

Soteria contributes towards the reduction of carbon emissions as it consumes only 35% less power than state-of-the-art HPC Accelerator.