Welcome to WordPress. This is your first post. Edit or delete it, then start writing!

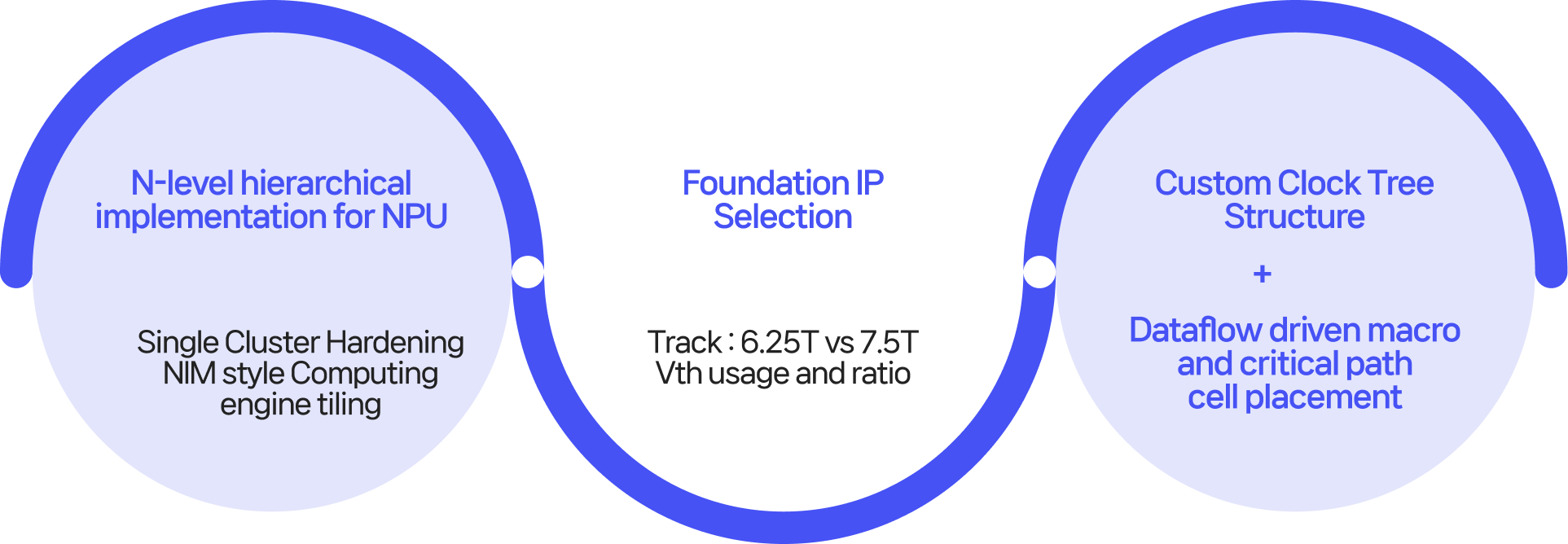

Cutting-edge Hyper-Scale AI Acceleration

Eco-Friendly ASICs Transforming the Cloud

info@soteria-sys.com

Cutting-edge Hyper-Scale AI Acceleration

Eco-Friendly ASICs Transforming the Cloud

info@soteria-sys.com

8th Floor, JLK Tower, Yeoksam-dong 678-29, Gangnam-gu, Seoul, South Korea

1290 Reamwoo Ave., Sunnyvale, CA 94089, USA

Hi, this is a comment.

To get started with moderating, editing, and deleting comments, please visit the Comments screen in the dashboard.

Commenter avatars come from Gravatar.