We Build

Future

Technology

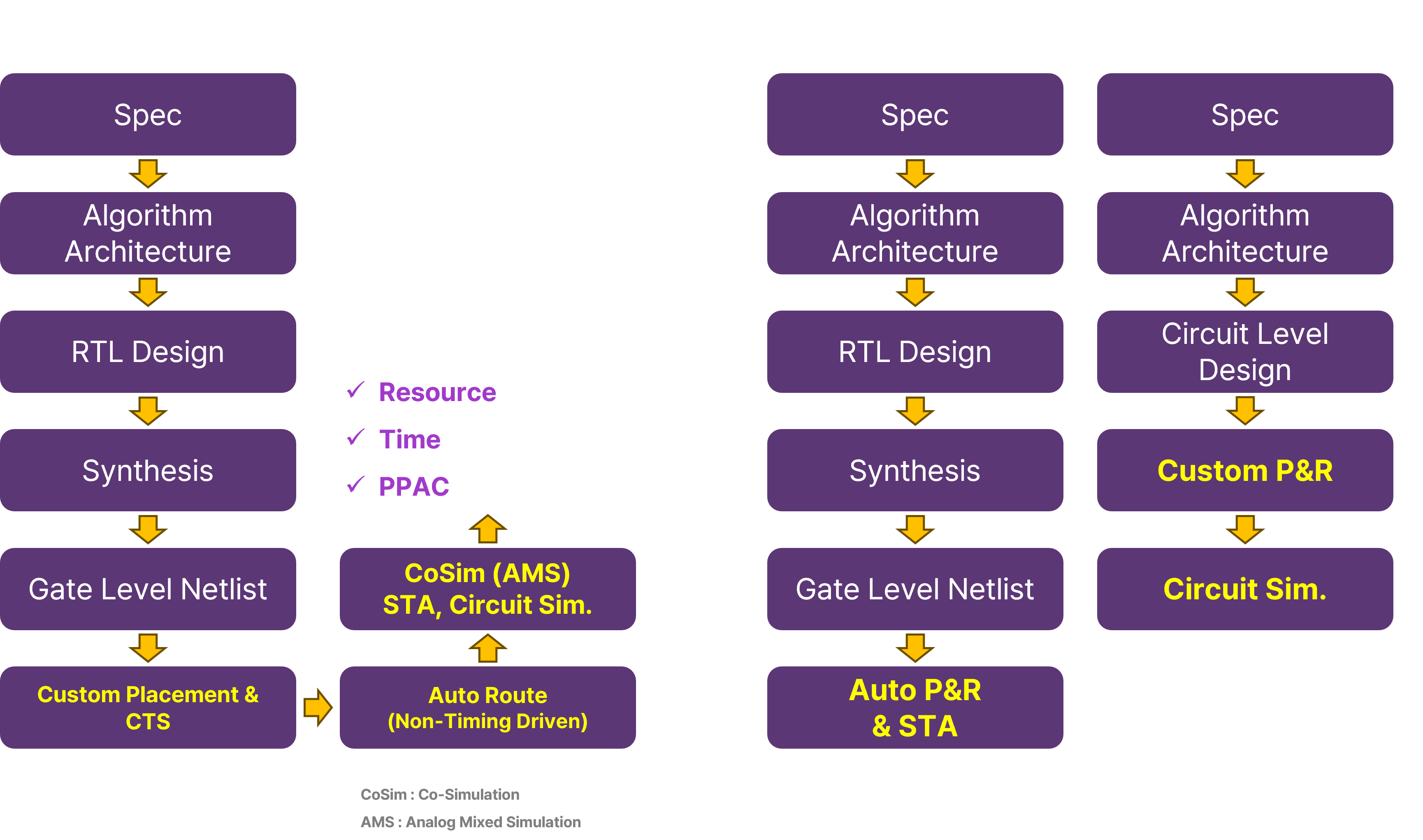

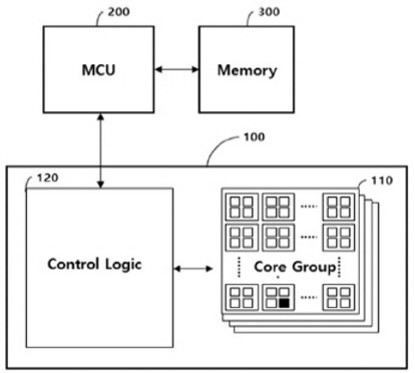

Birthed from the cradle of innovation, the Georgia Institute of Technology, we are pioneers in energy-conscious high-performance, massively parallel computing and dependable AI ASIC Cloud systems. In collaboration with global AI Transformers, SoC conglomerates, and Eco-friendly Data Centers across Europe and North America, we are co-creating the future of technology. Our expertise lies in crafting state-of-the-art semiconductor chips and high-performance computing accelerators.

Embracing the slogan ‘Energy for Velocity, Potential Unlimited’, we commit to relentless innovation and technological advancements, propelling us as industry leaders.

OUR CLIENTS WANT

THEIR OWN CHIPS.

Kim James Jongman

– Seoul National Univ. Department of E.E.

– Doctorate Degree in Pennsylvania

– Georgia Tech Professor

– Computer Architecture & AI

– Sogang University Bachelor in Computer

– Engineering, Masters at KAIST

– Doctorate Degree in Pennsylvania

– Oak Ridge National Lab

– Sogang University Professor

– Georgia Tech, Ph.D.

– Firmware, System SW

– Founder and CTO of Air Defense, Acquired by Motorola

– KAIST, Sungkyunkwan University, Master of Electrical Engineering

– Soc Chip Design

– Samsung Electronics, Hynix 25+ Years of Experience

– KAIST, Ph.D. in Electrical Engineering

– Intel PSG (San Jose, CA)

– Missouri University of Science&tech assistant professor

– Samsung Electronics DRAM design

– SK Hynix DRAM NAND design

– Chonnam national university, TJUFE MBA

– Samsung & DSP

– Technical Marketing

– Seoul National University, BS/MS Computer Engineering

– SoC Architectural Design

– Samsung Electronics

– Georgia Tech Ph.D. ECE Professor at UTSA & Korea Universoty

– Sungkyunkwan University, Master of Electrical Engineering

– Physical Design

– Samsung Electronics, 22+ Years of Experience

– Kyungpook National University, Master of Physics

– Samsung Electronics, 28+ Years of Experience

– Device, FINFET