CONTACT US

KOREA

8th Floor, JLK Tower, Yeoksam-dong 678-29, Gangnam-gu, Seoul, South Korea

info@soteria-sys.com

+82-70-4834-1130

USA

1290 Reamwoo Ave., Sunnyvale, CA 94089, USA

+1 216-687-4862

CONTACT

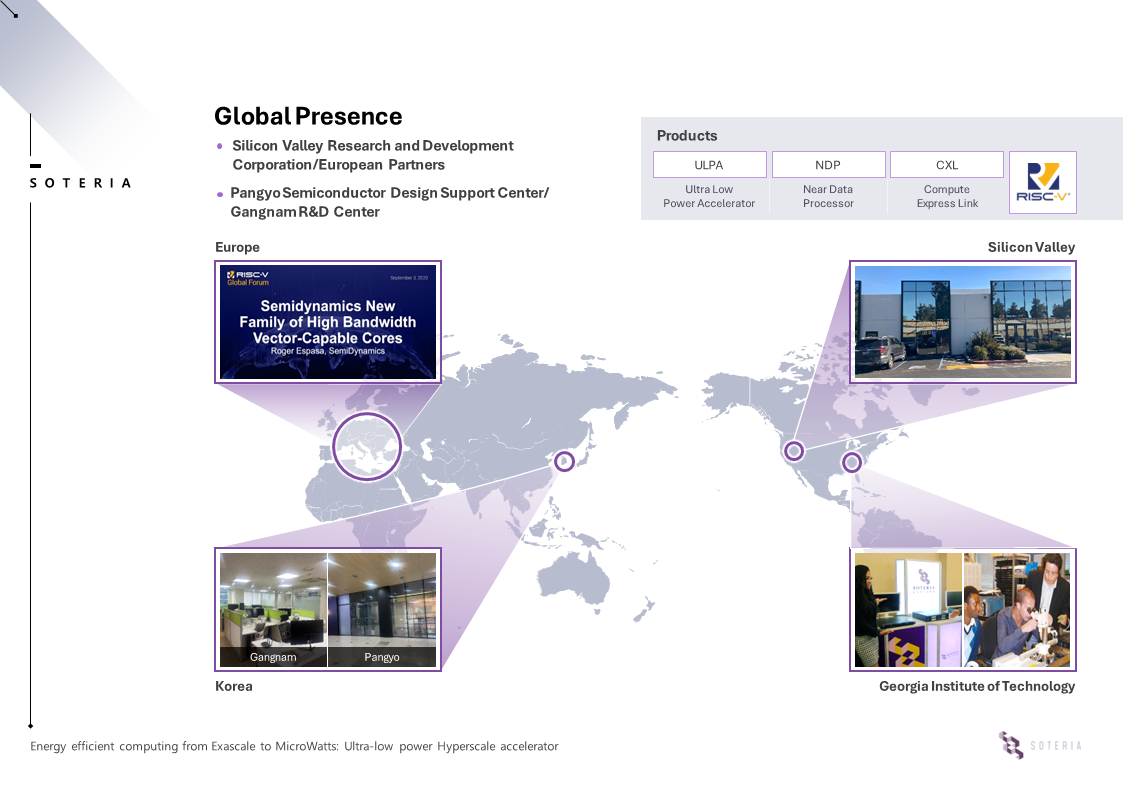

GLOBAL

PRESENCE