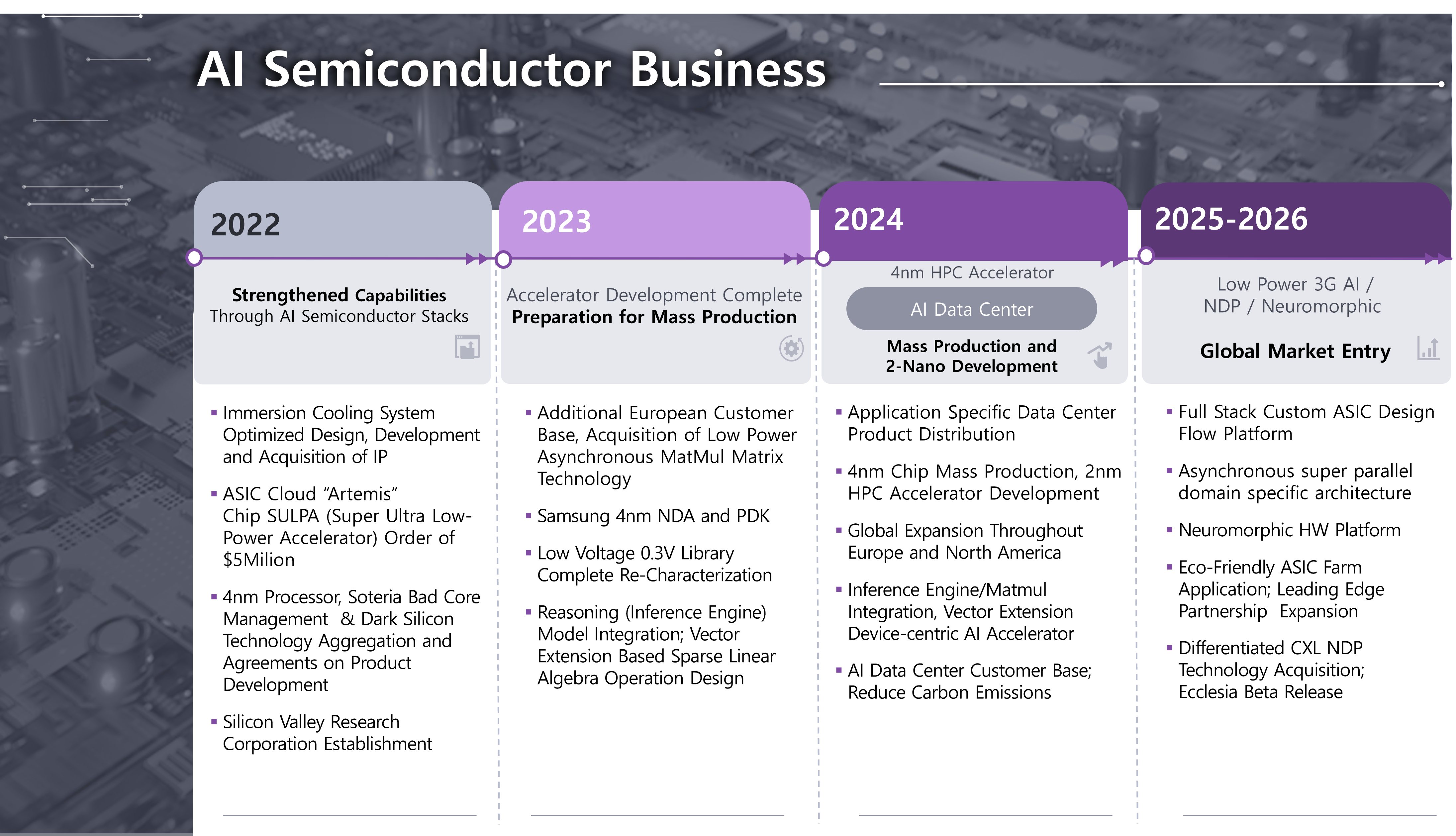

The Future of ASIC Cloud

Begins Here Beyond Imagination

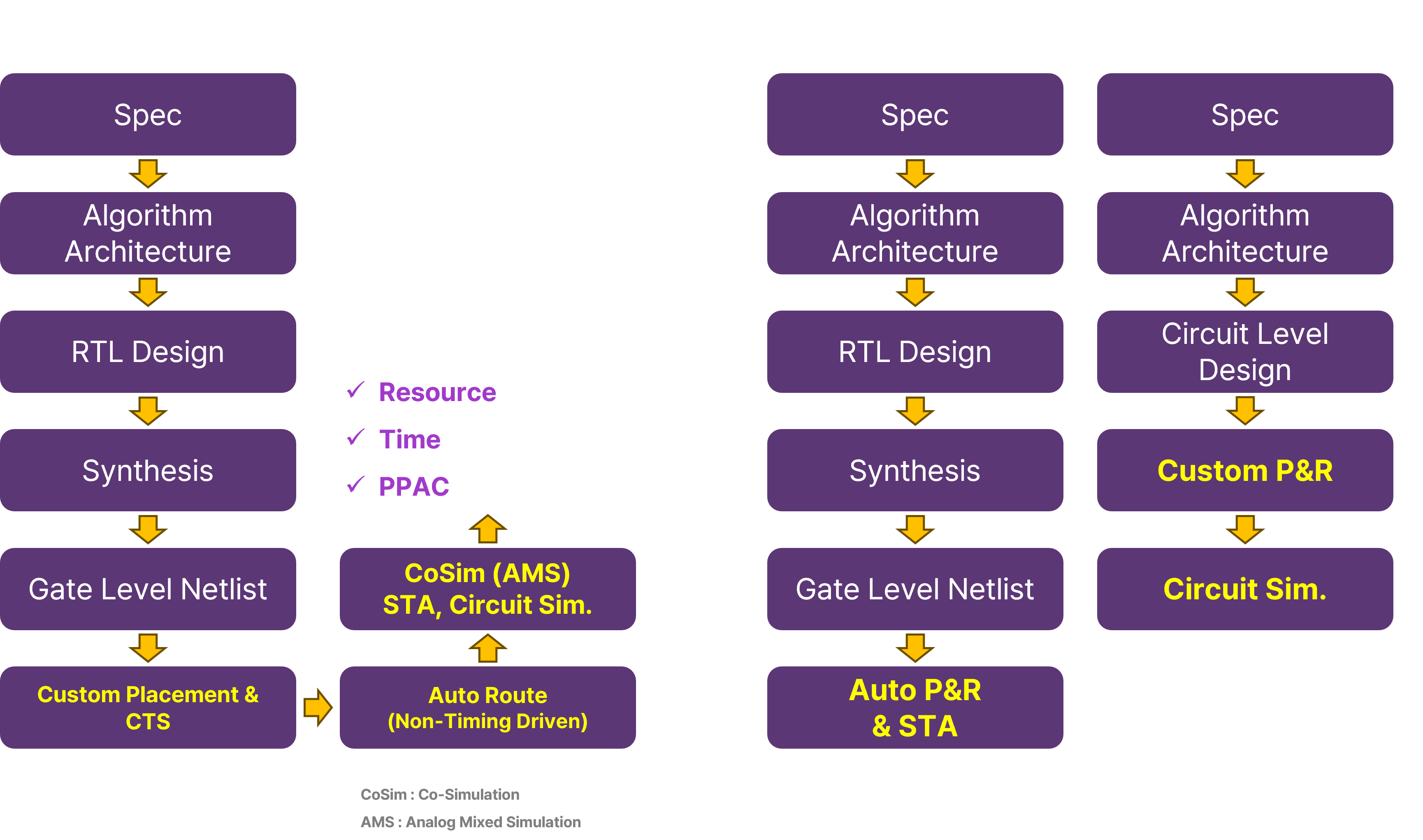

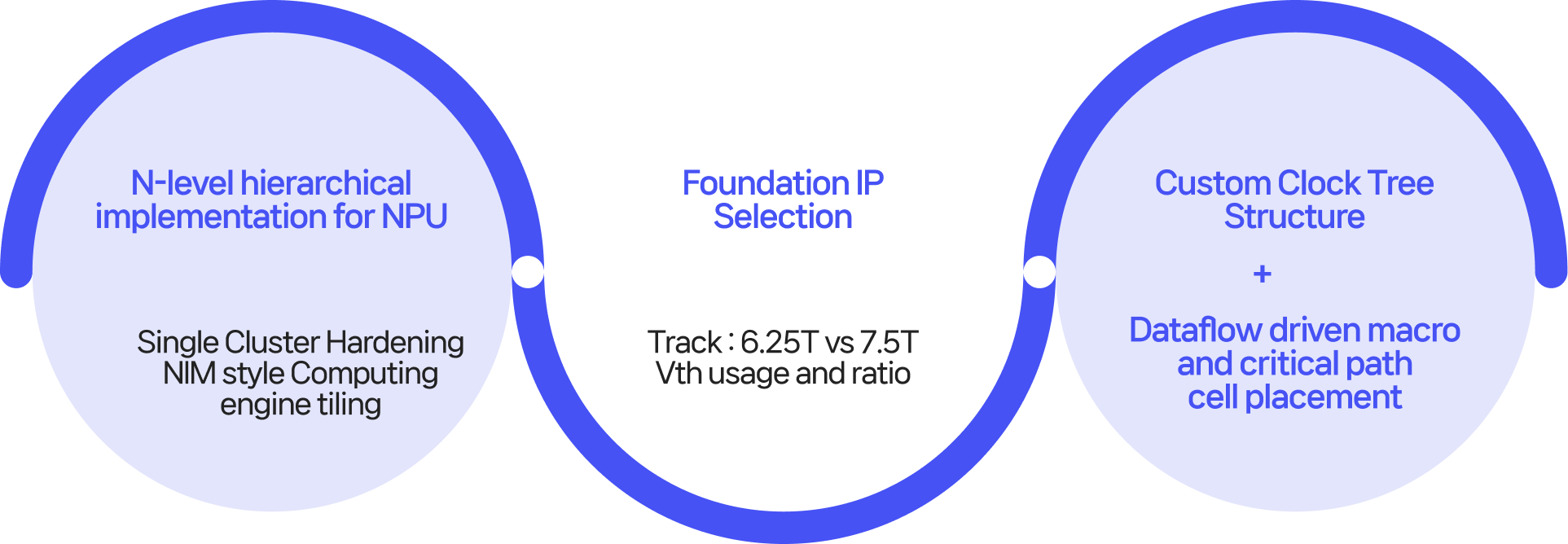

ASIC Accelerator Challenges and Innovations

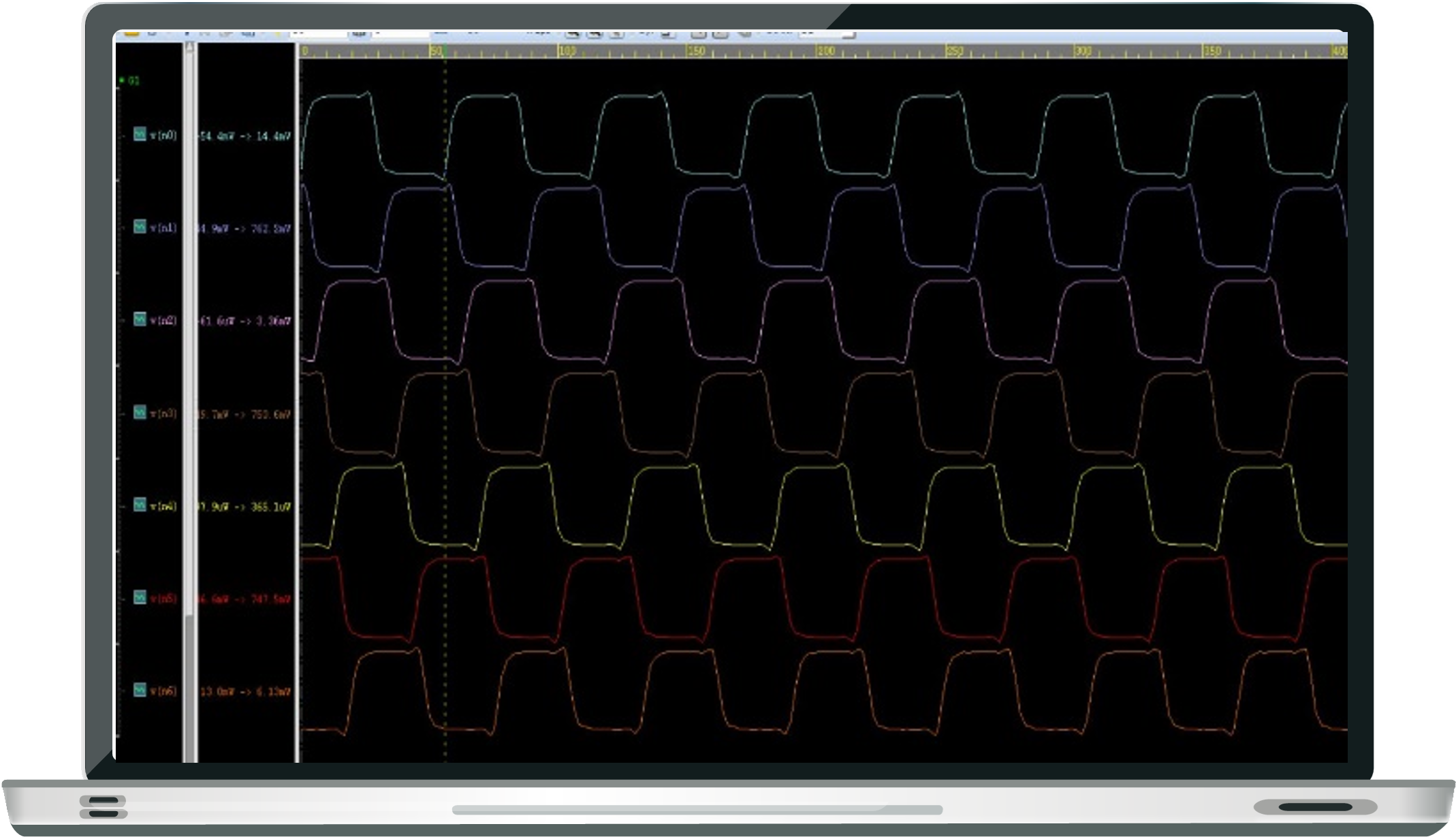

Low noise

Fully differential

Ultra low power

Intricate matching scheme

Soteria’s Various Models

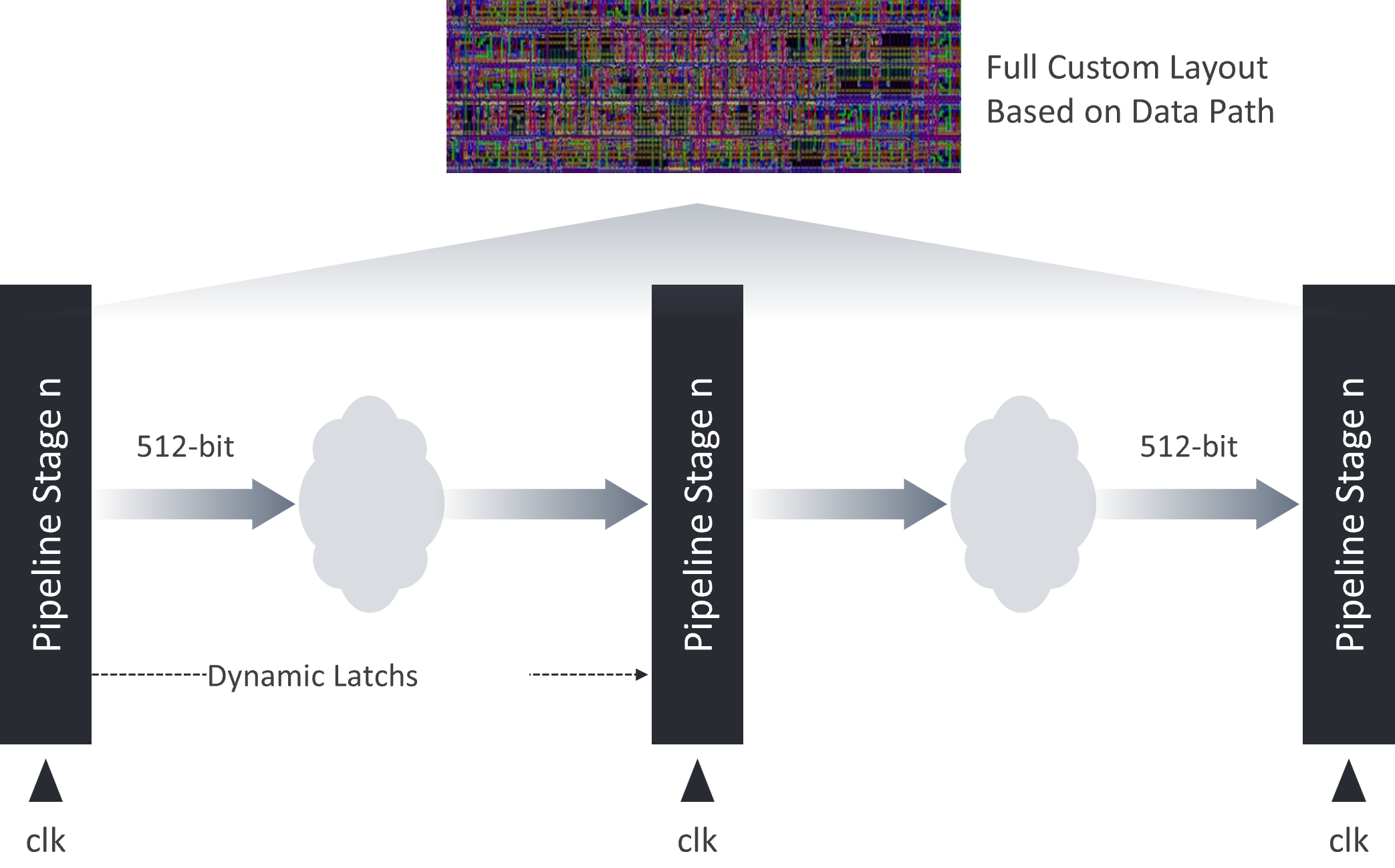

• Ultra Low-voltage cells (Near-threshold cells)

• Special-purpose cells (Pulse-based, Multi-bit, Mixed-Vth)

• Layout-optimized cells (Multi-height PMK, Input sharing)

• Synthesis-friendly cells (Variable skews, Multi-setup/delay)

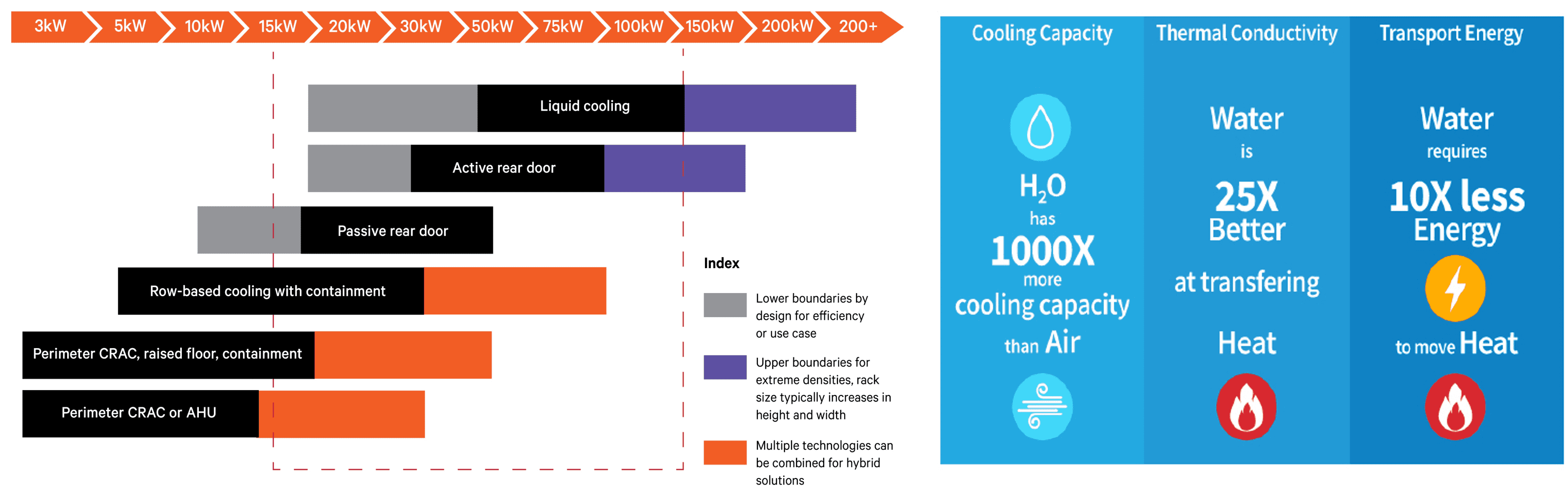

By providing an integrated system that considers both Immersion Cooling systems optimized for the data center environment and AI ASIC accelerators, efficiency and performance are maximized.

Interfacing with software equipped with management and monitoring functions, it supports the efficient operation of data centers.

The energy demand for data centers has exploded, consuming up to 5% of the world’s energy demand in 2025. Our company’s custom HPC accelerator, optimized for liquid cooling, is a future-leading technology that can solve this problem.

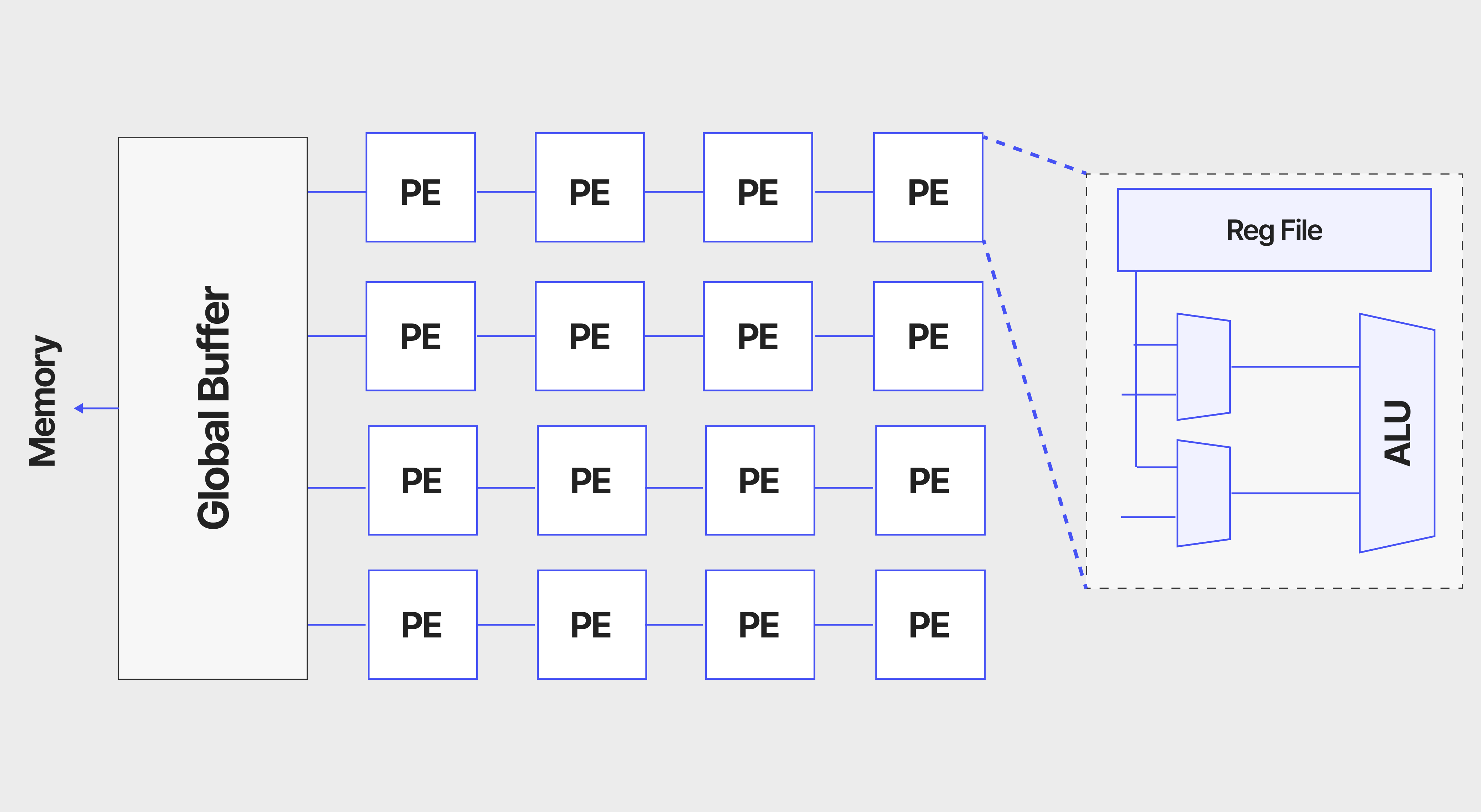

Amplifying the prowess of ultra-parallel HPC development, we’ve fine-tuned the architecture and design of AI ASIC accelerators, catapulting performance and energy efficiency to unparalleled heights.

Leveraging Workload Specific algorithms and cutting-edge optimization techniques, we’ve achieved a monumental leap in computational throughput.

We’ve engineered a dedicated hardware function for neural network acceleration, fortifying its integration or connectivity with existing System-on-Chips (SoCs)

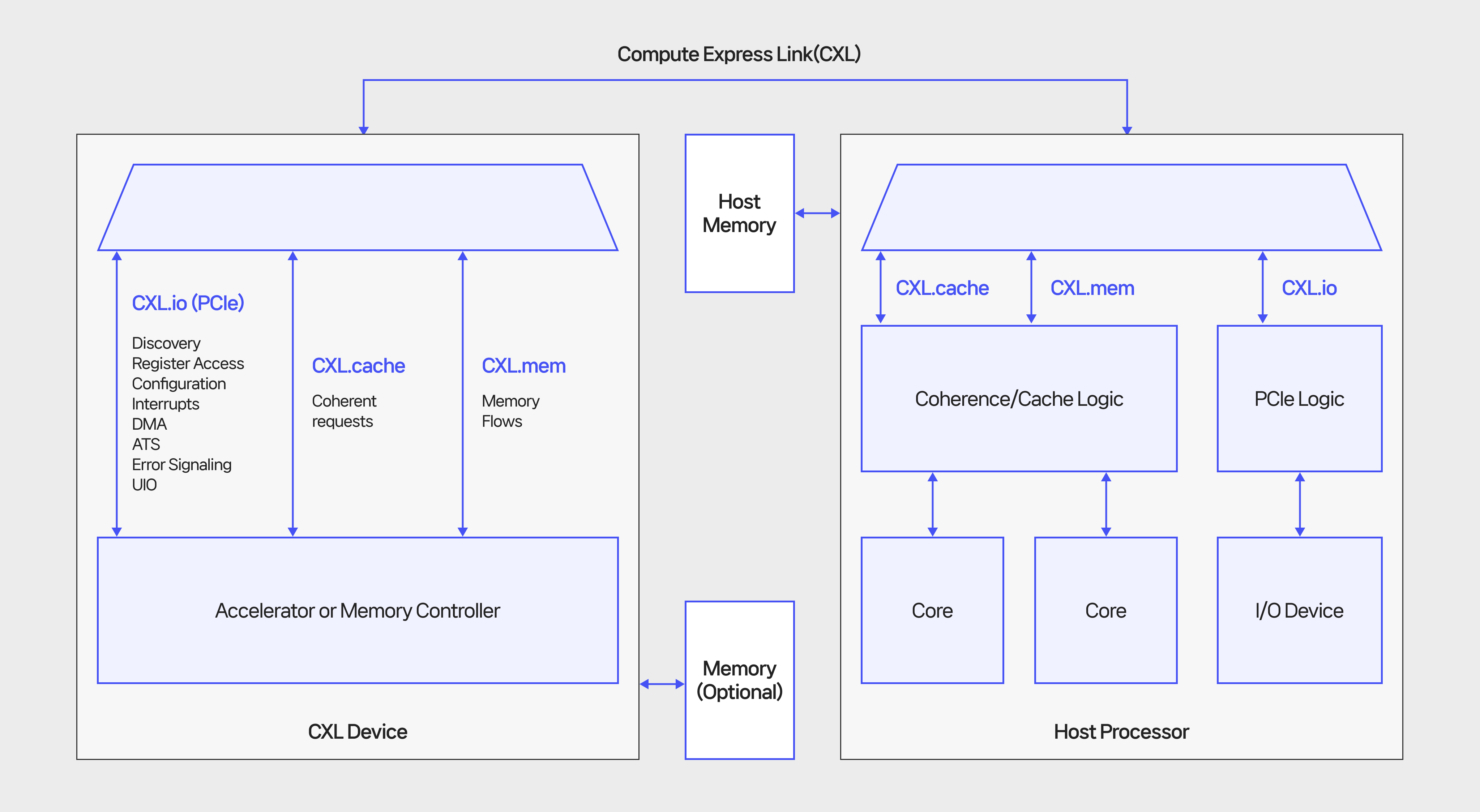

Our system can reduce learning time in evaluation using various types of recommender system models compared to the latest system that connects large capacity new memory based on existing PCIe technology.

It helps improve computing performance by connecting accelerators, memory, and storage devices used with the CPU, and is a method of solving data processing delays, slowdowns, and scalability problems in existing systems.

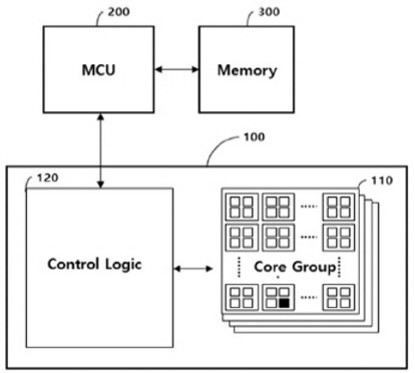

NDP-CXL CHIP

Architecture

Our system overcomes the limited performance limitations due to low bandwidth and memory capacity through CXL’s wide bandwidth and memory expansion capabilities.

By deploying an NDP module specialized for computation, data transmission overhead required during the computation process is reduced.